Intel this week signaled research advancements for its tri-gate transistor technology, indicating that along with other emerging methods and manufacturing, it has a technology trifecta lined up for tomorrow’s energy efficient chips.

Intel researchers said the technologies — tri-gate insulation, high-k gate dielecrics and metal gate electrodes, and strained silicon — will allow the company to push performance and prevent power leakage while continuing the march toward smaller and smaller transistors, which become increasingly difficult to control and can consume more energy with traditional approaches.

“Because of the nature of the technology, it becomes more compelling as time goes on,” Intel Director of Components Research and Technology and Manufacturing Group Vice President Mike Mayberry told TechNewsWorld. “This really solves the problem as some [transistor] node devices get smaller and smaller.”

Next-Gen Ready

Intel could manufacture chips using the tri-gate and other technologies today, but will likely hold off at least until the move to 32-nanometer manufacturing in 2009, or the introduction of even smaller 22-nm technology in 2011, Mayberry said.

“It’s reached a level of maturity so it’s available as a development choice,” he said.

Intel has previously discussed its tri-gate approach — a way of wrapping transistors in a sort of insulation tunnel — and has been working on the technology since 2002.

“Now, we’ve added the high-k as well as the strained silicon,” Mayberry said.

Evolution Over Revolution

The tri-gate technology was introduced a few years back as a way to head off energy and control issues of smaller transistors, but it has been put off by significant advances in strained silicon technology, which represents a shorter-term, but less radical industry change, IC Insights Vice President of Technology Trevor Yancey told TechNewsWorld.

“If at all possible, integrated circuit manufacturers will use an evolutionary-type advancement rather than a revolutionary type, and multiple-gate transistors are a revolutionary improvement,” he said.

Strained silicon, a different way to architecture chip and transistor structure, has turned out to be an “engineering feat,” according to Yancey.

However, he also highlighted the need for technologies such as Intel’s tri-gate, since current methods “will eventually run out of steam.”

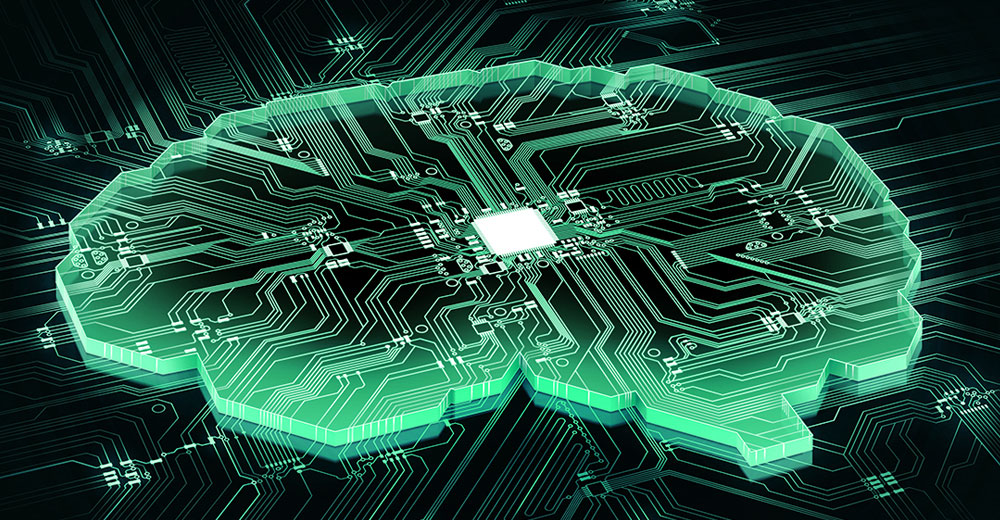

Chips in 3D

Intel touted its tri-gate geometry, claiming the insulation on three of four sides of the transistor would deliver a 45 percent increase in speed and a 35 percent reduction in power consumed compared to today’s leading 65-nm transistors.

As transistors become smaller, it becomes harder and harder to keep them working right, Gartner Vice President Martin Reynolds told TechNewsWorld.

He said the real key to Intel’s tri-gate technology is that it introduces three-dimensional (3D) architecture by building up on silicon, likening such structure to a cake, compared to a pizza.

“This absolutely will be needed to keep silicon moving,” Reynolds said.