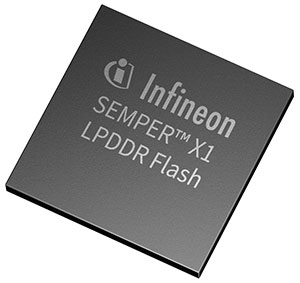

Infineon Technologies last week introduced the automotive industry’s first LPDDR Flash memory to support the development of new E/E (electrical and electronic) systems for semi-autonomous vehicles. Safe, dependable, and real-time code execution, which is essential for automotive zone and domain control, is provided by the Infineon SEMPER X1 LPDDR Flash solution.

According to Infineon, the device enables 20 times quicker random read transactions for real-time applications and performs eight times better than conventional NOR Flash memory. Characterizing this type of performance improvement as remarkable is not hyperbolic.

Typical NOR Flash memory is often called non-volatile storage, meaning that storage devices with that type of flash memory retain the data without using a battery or other powered voltage supply. This capability has made it possible for software-dependent cars to offer cutting-edge features with improved security and architectural flexibility.

Next-Gen Cars Are Computers on Wheels

As I’ve observed in previous columns, modern cars have evolved into computers on wheels over the past 20 years. Next-generation cars depend on cutting-edge multicore computers created using modern manufacturing techniques.

Because intelligence and real-time connectivity are needed to satisfy the need for safety and dependability in autonomous driving scenarios, higher-density integrated non-volatile memories are no longer a financially viable alternative. However, these sophisticated automotive real-time computers require more extraordinary performance than is offered in current memory solutions.

Infineon created SEMPER X1 with a proven LPDDR4 interface running at 3.2 GB/second and a multi-bank architecture to address domain and zone controller performance and density needs.

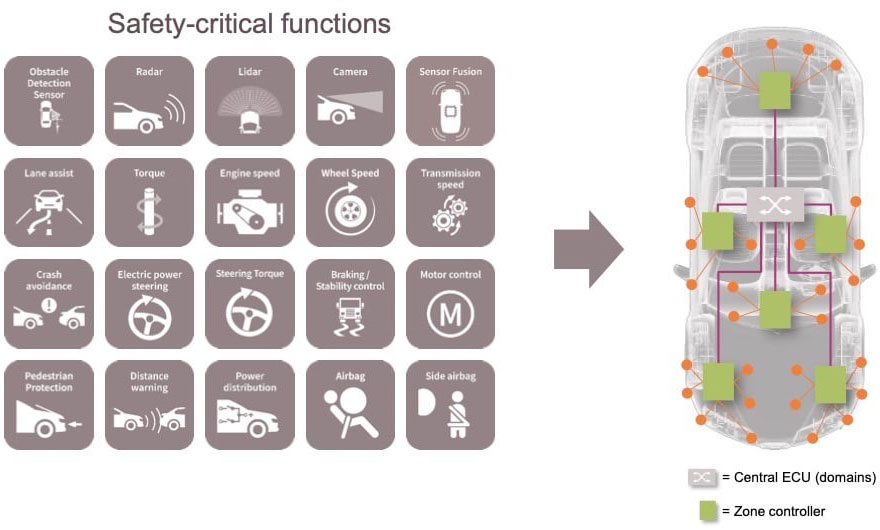

Traditional safety-critical functions in a next-gen car (Source: Infineon Technologies)

The resulting value proposition is quite compelling. Infineon couples flash memory with an LPDDR (Low Power Double Date Rate) interface to allow more dramatic performance and scalability than xSPI NOR flash to satisfy the new requirements of automotive zone designs. The choice by Infineon to utilize this interface is smart, given that the interface has been on the market for years and has a low-risk implementation reputation.

From a vehicle standpoint, the transition to software-defined vehicle architectures has caused a memory challenge for next-generation auto designs. Traditional xSPI NOR Flash memory is inadequate for several reasons, cost being a primary one. SEMPER XI leverages the LPDDR interface method from the DRAM industry to address new computing requirements in the automobile industry.

Key Automotive Asks: Growing Performance, Density Demands

Next-generation semi-autonomous automobiles increasingly require more flash memory and quicker performance. Cars have been moving toward zonal designs with no-compromise real-time processing for some time. These demands for higher performance simply cannot be satisfied by what ordinary NOR flash storage provides today.

The increasing number of domain and zone controllers appearing in next-gen semi-autonomous vehicles must process enormous volumes of data in real time while consolidating numerous safety-critical operations.

These zone controllers have intense real-time computing needs. While these controllers send information to the main ECU (Electronic Control Unit), these zonal controllers must also manage steering, engine, and other critical safety functions.

Automotive zone controllers are constantly being pushed to provide greater performance levels to fulfill these real-time processing requirements. A controller with integrated embedded memory on board simply cannot handle this heightened level of complex processing.

Quicker Access to External Flash Needed

The processing requirements of next-generation automobile designs have induced a shift away from real-time processors with few CPU cores and onboard flash. At a high level, one can reasonably state that the evolution of semiconductor technology has caused a mismatch between the CPU and memory.

Given the cost pressure in the smart car and EV markets, adding onboard flash isn’t economically viable utilizing today’s advanced semiconductor process nodes employed by those processor solutions.

The reality is that fast, real-time multicore processors, which operate from external flash memory, are necessary to meet the requirements of next-generation automotive designs.

Automotive-qualified embedded flash technologies have difficulties with high cost (large die areas) and lack of scalability at advanced manufacturing nodes. In addition, the industry requires additional flash memory to accommodate the expanding code size and complexity.

xSPI Is Unscalable and Runs Out of Gas

All these factors appear to have influenced Infineon’s role in developing LPDDR Flash memory.

Infineon VP of Marketing and Applications, Sandeep Krishnegowda, has been clear that the company utilized high-profile OEM feedback to help define the LPDDR memory category as the right solution to address the increasing need for real-time compute capability for code execution by multicore processors. This approach makes sense as fast random access is at the heart of LPDDR flash.

Undoubtedly, this method accelerates execution rates. According to Infineon, when compared to a typical Octal (x8) xSPI NOR flash chip, using LPDDR flash provides a stunning 20x increase in performance. Conversely, this performance improvement is needed to toggle from the real-time computations inside the CPU to those in external memory.

With its LPDDR interface, the SEMPER X1 flash can deliver throughput rates of up to 3.2 GB/second. Its multi-bank design permits over-the-air firmware changes with no downtime, which is critical in autonomous driving scenarios. The device also includes enhanced error correction and other safety measures, and it complies with ISO 26262 ASIL-B.

Other factors come into play driving the replacement of xSPI with LPDDR flash.

First, xSPI, as a legacy interface, is not only too sluggish but doesn’t scale adequately from a future needs standpoint. This critical factor is also driving demand for LPDDR flash. Further, xSPI devices on the market today use a low voltage complementary metal oxide semiconductor (LVCMOS) approach that can’t scale beyond 200MHz, prompting the need for a solution with higher bandwidth.

Given that context, conventional Octal xSPI flash devices are unsuitable for code execution because they cannot accommodate today’s gigahertz multicore processors.

Closing Thoughts

Infineon’s SEMPER X1 is an essential step in that direction as it facilitates more complex engine control and real-time decision-making bolstered by a memory architecture that can grow independently of the CPU.

This new non-volatile memory category will be fascinating to watch as the ecosystem grows. My recent podcast with Krishnagowda provides some intriguing insight into what he believes are the disruptive implications of this new announcement.

Infineon has been a bit cagey about market categories beyond the auto space that LPDDR Flash memory might appeal to.

Linus Wong, Infineon’s Director of Product Management for SEMPER X1, acknowledges that warehousing, security, and medical applications may see tremendous interest in this new storage capability. “When we look at these secondary markets, it really comes down to the enhanced value proposition for [usage models] that can exploit latency improvements measured in the thousands of a second,” he said.

Finally, it’s not insignificant that Infineon has taken an industry leadership role in releasing this new memory solution. The company’s gravitas, long-time reputation for design-in excellence, and history of solid execution that is crucial with high ASP next-gen autos are all tailwinds that favorably support market acceptance of LPDDR Flash memory.

According to Infineon, SEMPER X1 is now undergoing sampling, with a commercial release scheduled for some time in 2024.